雷鋒網AI科技評論按:第27屆現場可編程邏輯與應用國際會議(The International Conference on Field-Programmable Logic and Applications,FPL)九月份在比利時根特召開。在FPL 2017上,一篇來自德國卡爾斯魯厄理工學院(Karlsruhe Institute of Technology)的論文《Voltage Drop-based Fault Attacks on FPGAs

using Valid Bitstreams》獲得了最佳論文獎,同時也成爲了所有與會者談論的焦點。

本文作者@小哲打豆豆爲雷鋒網(公衆號:雷鋒網)專欄作者,目前在多倫多大學電子工程系就讀博士,以下爲作者對於本篇論文的介紹。

背景介紹

FPGA(Field Programmable Gate Array,現場可編程邏輯門陣列)因爲其卓越的靈活性而越來越受到用戶青睞。不論是低端的IoT設備,還是高端的雲計算中心,FPGA在這些最新的應用場景下都展示出高效的計算能力。加上過去就一直在應用FPGA的關鍵行業,例如軍工,航空航天等,諸多領域的發展都給FPGA的安全性帶來了新的挑戰。

之前對FPGA攻擊的研究都是基於本地的,例如,更改FPGA的電源或時鐘,或在管腳人爲注入「特洛伊代碼」。隨着FPGA越來越多的在雲計算中心中的應用,任何人都可以遠程在服務器的FPGA上佔用一部分邏輯門,將這個區域設置爲自己需要的任意電路,以實現運算加速等功能。而之前,FPGA只能通過受信任的IP提供者被設置。這意味着FPGA在雲計算這類應用中將前所未有的暴露自身的安全漏洞。

這項研究的威脅模型基於以下假設:攻擊者可以重構部分或全部FPGA的邏輯門,目的是對系統發起DoS(Denial of Service)攻擊。作者對兩種FPGA分別進行了測試,一類是在雲計算中心作爲加速器的FPGA,另一類是有片上SoC的FPGA,這類FPGA多應用在IoT場景下。對兩種FPGA的研究都發現,發動的DoS攻擊可以使FPGA完全癱瘓直至手動復位電源。對於有片上SoC的FPGA來說,在其應用場景下可能並沒有電源復位的選項,唯一復位電源的的辦法只能是將電池取出再放回。

電路設計

針對FPGA的DoS攻擊的基本原理大致如下:通過編輯片上邏輯,使FPGA負載能在瞬間改變。由於電源瞬態響應緩慢,以及電源分配網絡(Power Delivery Network,PDN)的設計缺陷,導致FPGA電壓過低,進入欠壓保護而被鎖定,進而達到癱瘓設備的目的。

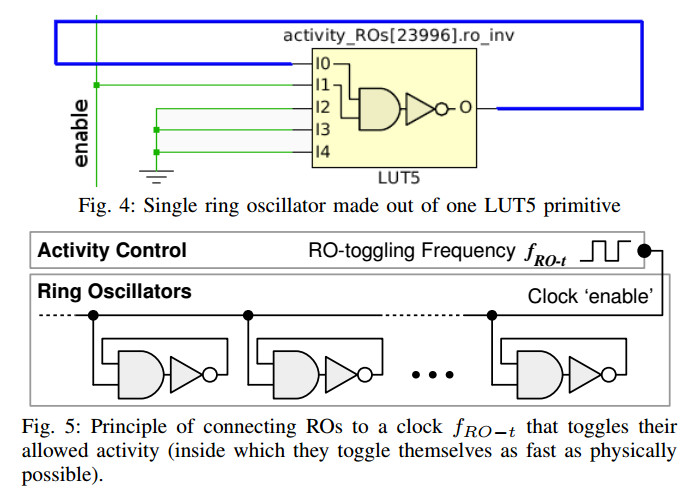

爲了達到瞬間改變FPGA負載的效果,作者將一個邏輯單元的輸出經過一個非門連回到輸出端。如下圖所示,這樣的電路構成了一個正反饋的環形振盪器(Ring Oscillator)。環形振盪器裏的CMOS開關管會以極快的速度翻轉,消耗大量電流。大量邏輯單元都被設置成這樣的環形振盪器,並且通過一個使能信號控制所有振盪器,就能瞬間改變FPGA的電流負載。通過控制使能信號的開關頻率fRO-t,可以模擬不同的負載變化來觀察其對FPGA的影響。

實驗結果與討論

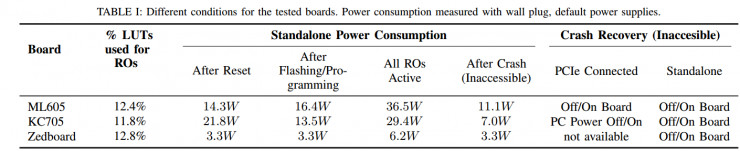

作者測試了三塊FPGA開發板,分別是:有40納米的Xilinx Virterx 6 FPGA的ML605開發板,28納米的Kintex 7 FPGA的KC705開發板,以及28納米的Zynq 7020 SoC-FPGA(雙ARM Cortex A9 + 片上FPGA)的Zedboard開發板。

測試中,三種開發板都在一定條件下發生了欠壓保護導致的系統崩潰。ML605和KC705在欠壓保護後均無法自動恢復。Zedboard則會隨機出現三種不同的系統故障:一是和前兩塊開發板一樣出現無法自動復位的欠壓保護;一種是芯片自動重置,片上所有的設置,包括兩個ARM核的狀態也被重置;第三種狀況類似重置,但是作者在試圖重新配置芯片時發生軟件故障,之後系統便進入第一種無法自動恢復的欠壓保護模式。可見,不論出現何種故障,都需要手動重置電源才能恢復系統。

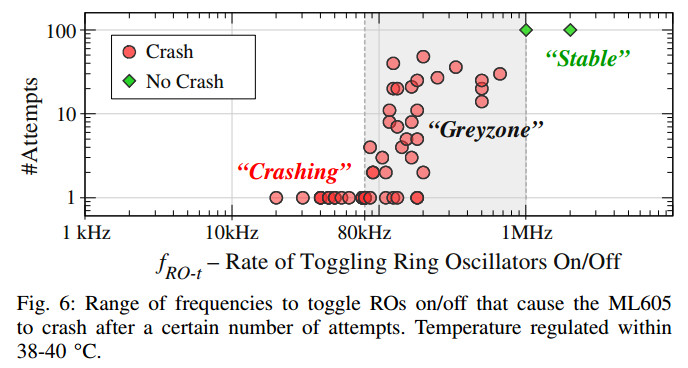

以ML605開發板作爲實例,作者在片上佈設了18720個環形振盪器,大約只佔用了12%的片上資源。使能信號的頻率fRO-t從20kHz到2MHz。實驗發現,在高於1MHz時,片上電壓壓降不足以引起欠壓保護;在80kHz到1MHz的範圍內,系統崩潰會隨機的發生;而在頻率小於80kHz時,系統崩潰幾乎必然發生。

作者同時將兩塊開發板通過PCIe接口接入工作站,發現系統崩潰同樣發生了。崩潰後ML605可以通過板上的電源開關進行復位,而KC705甚至必須要將整個工作站重啓才能恢復。下表總結了三塊板在不同狀態下的能耗:

以上實例展示了通過欠壓保護機制對FPGA發動DoS攻擊的方法。如此發動的DoS攻擊快速,且可以導致整塊FPGA不可逆的癱瘓,直至手動重置電源。

允許用戶自己設置FPGA實現運算加速的系統中,無疑暴露了巨大的安全隱患。這導致整臺服務器需要重新啓動。如果系統是通過不可替換的電池供電的話,FPGA將陷入永久的DoS狀態。

結論

FPGA在雲計算和IoT中都有大量的應用,在這些新的應用中,傳統的比特流加密(bitstream encryption)等安全措施已經不足以應對新的挑戰。在這項研究中,作者揭示了一個新的安全漏洞,通過一類方法可以對FPGA發動DoS攻擊,並在兩代FPGA上進行了實測。結果發現,僅僅利用12%的片上資源,就可以使FPGA由於欠壓保護而完全癱瘓。

雷鋒網AI科技評論獨家約稿,未經許可不得轉載。