前言:說起 FPGA,很多人可能都不熟悉,它的英文全稱爲 Field Programmable Gate Array,即現場可編程門陣列,也被稱爲可編程集成電路。隨着大數據以及 AI 的發展,越來越多的數據中心引入 FPGA 作爲 CPU 的加速器以提高數據處理速度,提升服務器性能,因此降低 FPGA 的能耗也成爲數據中心裏新的挑戰。本文介紹了其中一種降低 FPGA 能耗的方法——基於自測量的 FPGA 動態電壓調節解決方案。本文根據嘉賓的直播分享整理而成。

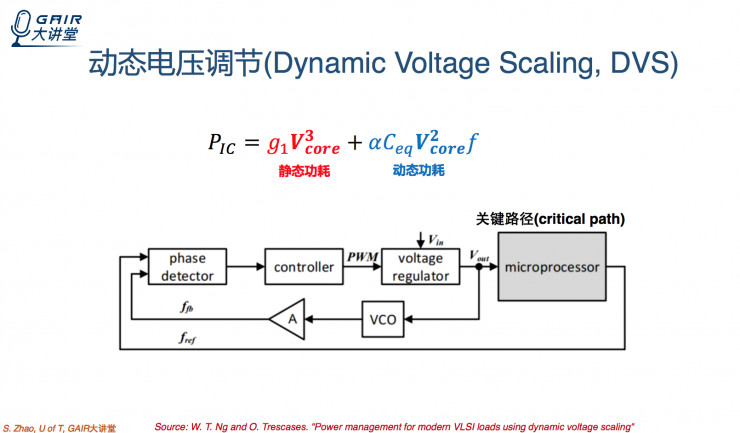

動態電壓調節(DVS)作爲常見的數字芯片節能技術,已經大量應用於 CPU 或 GPU 等芯片中。由於 FPGA 獨特的可編程硬件結構,它們的片上電路隨應用的改變而改變,這爲 FPGA 的動態電壓調節帶來了極大的困難。來自多倫多大學電子系的在讀博士生趙舒澤爲此提出了一種新的改進方案,有效地降低了芯片能耗並提升了性能。

趙舒澤,浙江大學電氣工程學院電力電子方向學士,多倫多大學電子系碩士,多倫多大學電子系博士在讀。研究方向爲 LED 光通信,諧振變流器,變流器的數字控制,以及電力電子在數據中心的應用。

分享提綱:

FPGA的簡介,FPGA的片上結構

FPGA的能耗

基於自測量的FPGA動態電壓調節(DVS)

分享內容:

大家好,我是趙舒澤,今天分享的內容是硬件方面我們的一些研究成果。接下來首先爲大家簡單介紹一下數據中心的結構以及能耗的問題,然後是關於 FPGA 的簡介以及 FPGA 在能耗上的挑戰。最後爲大家介紹的是我們團隊的研究成果,即如何在 FPGA 上實現動態電壓的調節。

數據中心的能耗

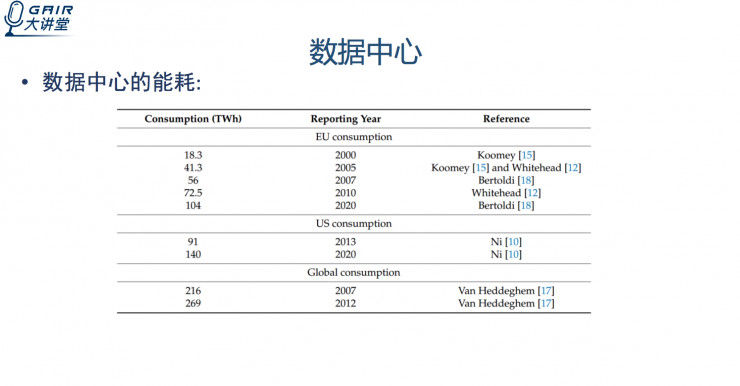

近十幾年,隨着信息技術的發展,尤其是最近非常火的大數據、雲計算、人工智能等這些方向的進展,數據中心作爲這些實現這些應用背後的大腦,無疑也是經歷了高速發展。隨着數據中心的集成度,計算能力的提高,數據中心的能耗也一直是一個非常棘手的問題。

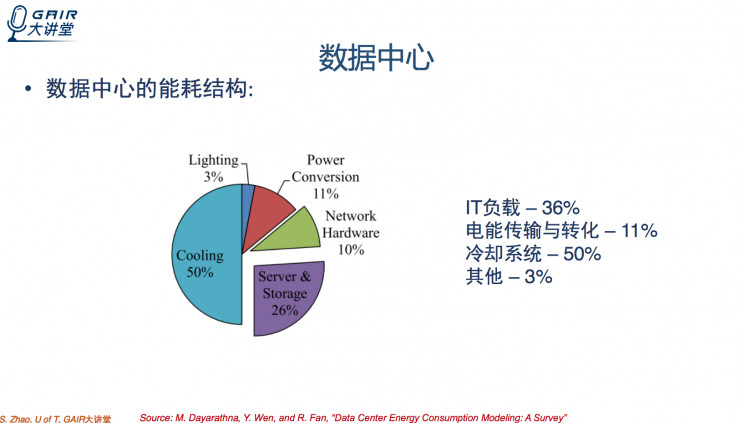

以美國爲例,2013 年數據中心的總能耗估計是 91 太瓦時(TWh),相當於一箇中等國家(例如菲律賓)全國的總用電量。要解決能耗問題,首先要看一下一個數據中心有哪些用電負載。

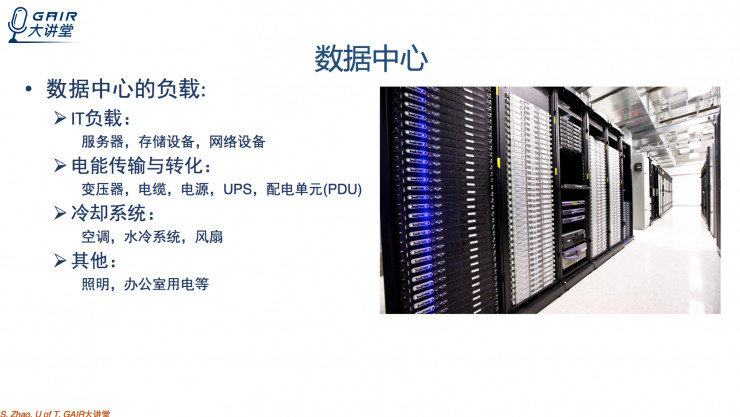

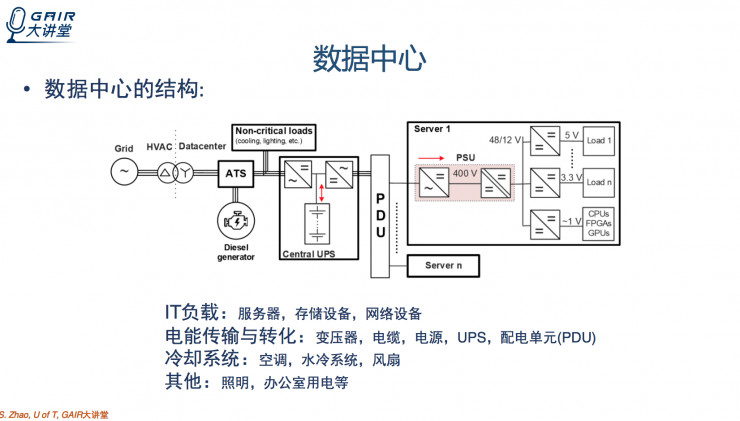

可以大致總結爲四類:IT 負載,包括服務器,存儲設備,網絡設備,交換機等;電能傳輸與轉化,包括變壓器,電纜,電源,UPS,配電單元等帶來的損耗;冷卻系統,包括空調,水冷系統,風扇等。其他,包括照明,辦公室用電等。

數據中心的結構

「ATS 自動轉化開關」的目的是:在電網出現問題時,可以自動轉換到柴油發電機組,這樣可以保證負載端不會出現斷電的情況。

「中心 UPS」有兩方面的作用。一方面可以保證輸送高質量的電能給IT負載,另一方面,在出現斷電的情況下,柴油發電機還需要一定的啓動時間,這段空檔由 UPS 來暫時供電,保證負載不會出現斷電的情況。

數據中心的能耗結構

每個數據中心的能耗其實很不同,這個圖只是一個平均值。IT 負載其實只佔到 36% 的能耗,電能傳輸與轉化大概佔 11%。其他有一半能耗都是被冷卻系統用掉的。也就是說爲了冷卻 IT 負載和電能傳輸與轉化所產生的熱能,需要消耗等量甚至更多的能量來冷卻數據中心,以保證正常工作。

如何降低IT負載中FPGA的能耗

FPGA 的中文名稱爲現場可編程邏輯門陣列。FPGA 在過去大量應用在消費電子產品,無線基站,軍事,醫療等高端應用場合裏,隨着大數據,人工智能的快速發展,我們對服務器的響應速度的要求不斷提高,CPU 已經被證明不太適合進行大量浮點運算,而 FPGA 的片上電路是可編程的,開發時間比較短,可以靈活的部署並且可以實現大規模的並行計算。由於這些原因,它開始被大量部署在數據中心裏作爲 CPU 的加速器,幫助數據處理以及計算,包括幫助網絡通信等等。

FPGA的優勢和劣勢

對於 CPU/MCU 這樣基於指令集的芯片來說,FPGA 有更大的靈活性,另外由於它是可編程的,可用最簡單的硬件架構來實現所需要的邏輯功能,因此更節省能源。

缺點是,在和特種芯片 ASIC 相比,速度較慢,能耗更高。ASIC 芯片內部架構雖較爲簡單,不可以硬件編程,只能用來專門處理某一種功能,靈活性最差,但是在執行某一種任務上的效率最高。

FPGA 芯片內部架構稍微複雜一些,可以硬件編程,因而可以通過硬件編程語言來改變內部芯片的邏輯結構,從而能夠在提供一定靈活性的同時,還能夠保證較高的處理效率,算是在靈活性和性能上取了個折中。

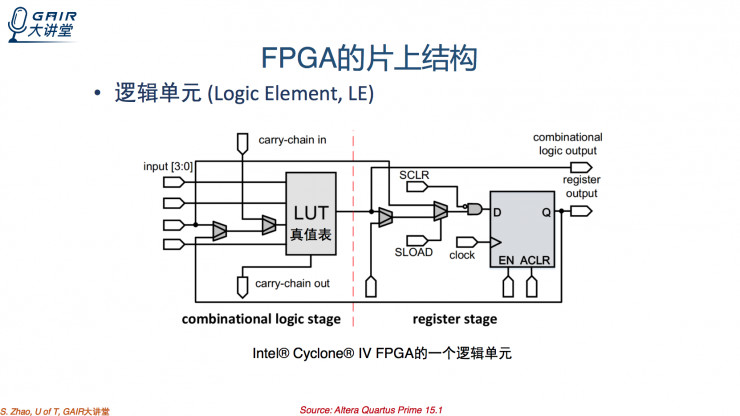

FPGA的片上結構

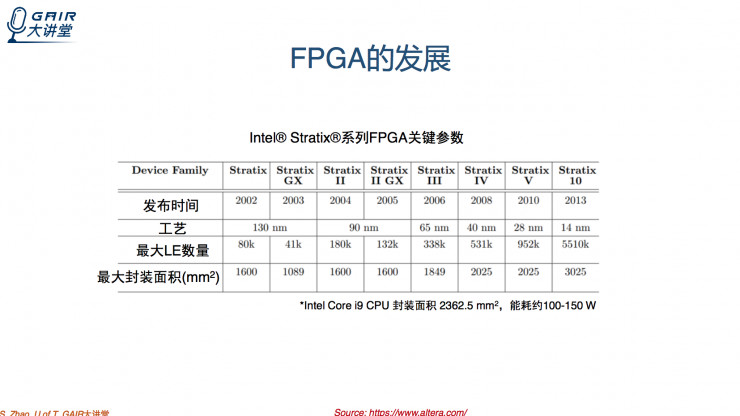

FPGA的發展

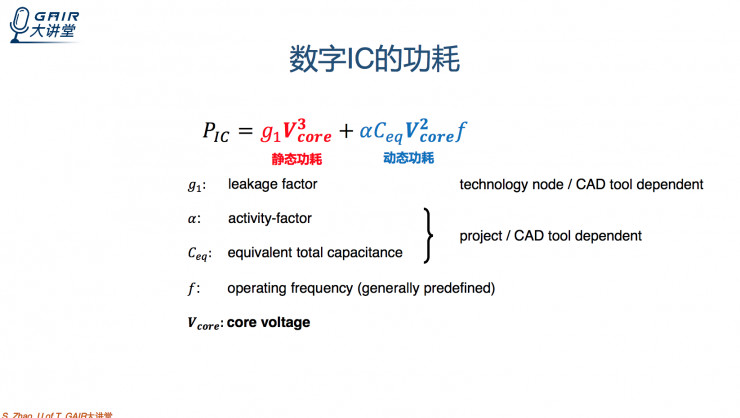

數字IC的功耗

動態電壓調節

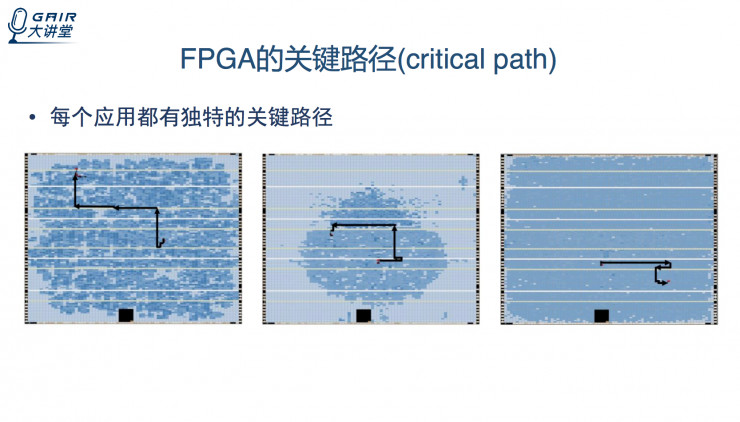

FPGA的關鍵路徑

每個應用都有獨特的關鍵路徑

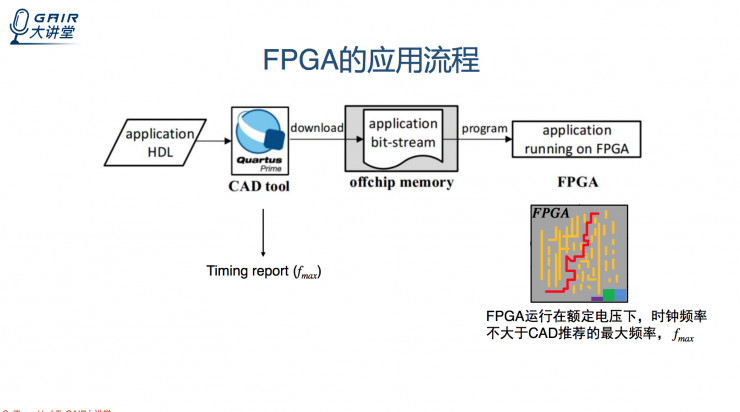

FPGA的應用流程

FPGA的的動態電壓調節

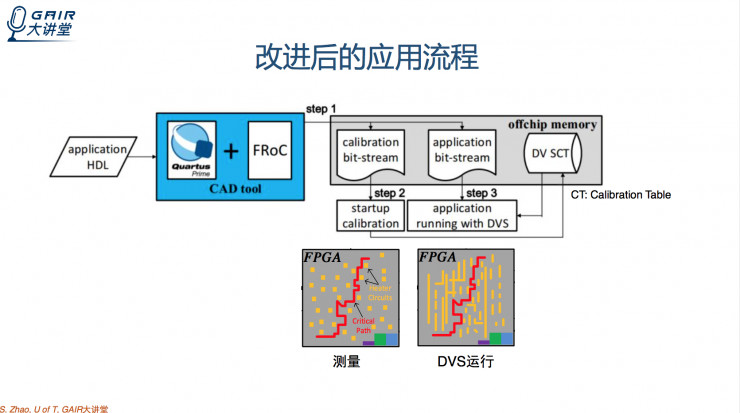

我們的思路是: FPGA 有不確定的片上結構,但是可以重複燒製。我們利用這個特點,把每一次的關鍵路徑都提前提取出來,把這些關鍵路徑單獨燒製在 FPGA 上,先測量這些關鍵路徑的延遲有多少,測完後把這些數據放在片外的存儲器裏。之後再將FPGA燒入用戶的應用,動態電壓調節的控制模塊會從剛測到的數據中找到當前溫度和頻率下最低的供電電壓是多少,然後電源按照這個電壓來給 FPGA 來供電。

改進後的應用流程

完整的流程圖解讀請看視頻回放。

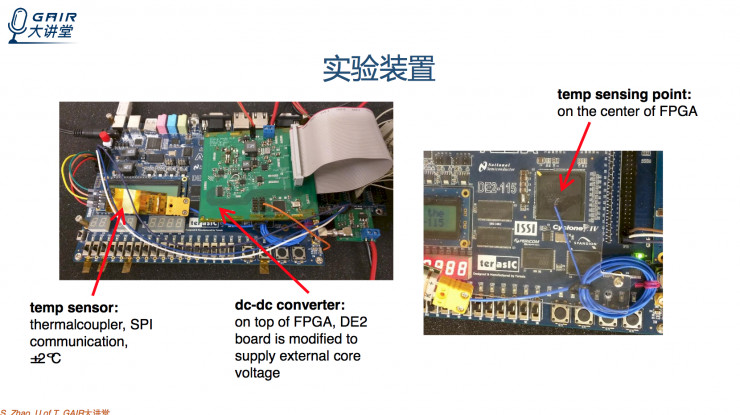

實驗裝置

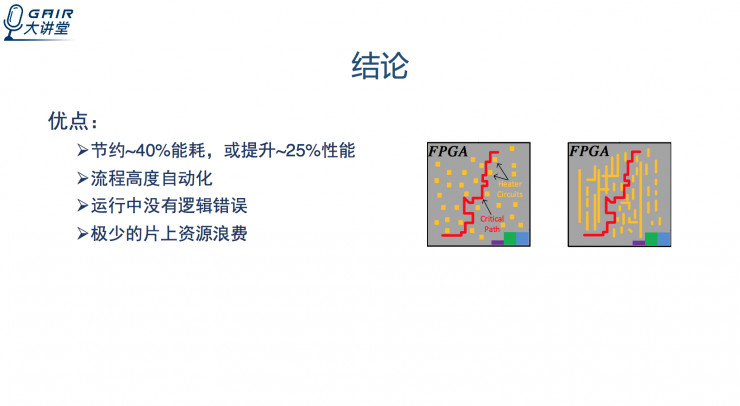

實驗結論

實驗流程及具體細節推薦觀看AI慕課學院:FPGA的動態電壓調節(DVS)——談談數據中心裏FPGA的節能。