雷鋒網 AI 科技評論按:6 月 2 日至 6 日,第 45 屆國際計算機體系結構大會(International Symposium on Computer Architecture,簡稱 ISCA)在美國洛杉磯召開。國際計算機體系結構大會(ISCA)是計算機體系結構領域的頂級會議。本次大會共收到 378 篇投稿,收錄 64 篇論文。

清華大學微納電子系博士生塗鋒斌在大會上做了題爲《RANA:基於刷新優化嵌入式 DRAM 的神經網絡加速框架》(RANA: Towards Efficient Neural Acceleration with Refresh-Optimized Embedded DRAM)的口頭報告。該研究成果大幅提升了人工智能(AI)計算芯片的能量效率。

塗鋒斌的研究論文是今年大會中國唯一被收錄的署名第一完成單位的論文。清華大學微納電子系尹首一副教授爲本文通訊作者,塗鋒斌爲本文第一作者,論文合作者還包括清華大學微納電子系魏少軍教授、劉雷波教授和吳薇薇同學。

Fengbin Tu, Weiwei Wu, Shouyi Yin, Leibo Liu, Shaojun Wei,「RANA: Towards Efficient Neural Acceleration with Refresh-Optimized Embedded DRAM,」International Symposium on Computer Architecture (ISCA), Los Angeles, USA, 2018.

清華大學微納電子系博士生塗鋒斌報告現場。

論文詳細信息如下:

1 研究背景

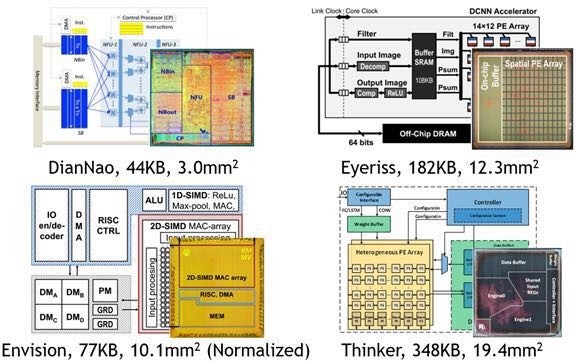

深度神經網絡(DNN)已經被廣泛應用在各種 AI 場景中。爲了獲得更高的精度,DNN 的網絡規模也日益增大,導致網絡數據存儲量達幾 MB 甚至幾十 MB。此數據量甚至會隨着輸入圖片的分辨率和批處理規模的增大而增大。然而,傳統的基於 SRAM 的 AI 計算芯片,由於芯片面積的限制,往往只有幾百 KB 的片上存儲容量。因此,在運行當前的 DNN 時,片外存儲訪問難以避免,這會造成巨大的系統能耗開銷。存儲問題是 AI 計算芯片設計中必須解決的一個重要問題。

當前幾款主流 AI 計算芯片(DianNao、Eyeriss、Envision、Thinker)及其存儲、面積參數。

2 數據生存時間感知的神經網絡加速框架(RANA)

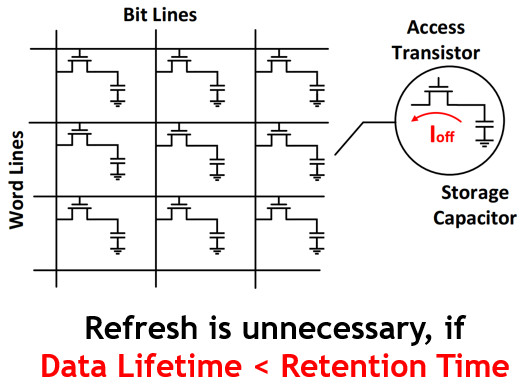

嵌入式 DRAM(簡稱 eDRAM),相比於傳統 SRAM 有更高的存儲密度,可以替代傳統 SRAM 作爲片上存儲以減少片外訪問。然而,eDRAM 存儲單元中的電容電荷會隨時間而逐漸丟失,因此需要週期性的刷新操作來維持 eDRAM 的數據正確性。已經有研究證明,刷新能耗是 eDRAM 總能耗的主要來源,而且會佔據整體系統能耗的很大比重。因此,使用 eDRAM 帶來的額外刷新能耗開銷不容忽視。本文發現,如果數據在 eDRAM 中的生存時間(Data Lifetime)小於 eDRAM 的數據維持時間(Retention Time),那麼系統將不再需要對於此數據的刷新操作。由此可以得到兩個優化方向:減少數據生存時間,和增大數據維持時間。

嵌入式 DRAM(eDRAM)結構及本文核心觀點。

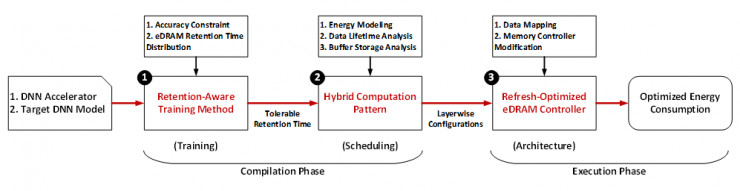

本文提出一種基於 eDRAM 存儲器的新型加速框架:數據生存時間感知的神經網絡加速框架(RANA)。RANA 框架採用 eDRAM 作爲片上存儲器,相比於傳統 SRAM 具有更高的存儲密度,大幅減少片外訪存。同時,RANA 框架採用三個層次的技術:數據生存時間感知的訓練方法,神經網絡分層的混合計算模式和刷新優化的 eDRAM 控制器,分別從訓練、調度和架構三個層面降低 eDRAM 刷新能耗,進而大幅優化整體系統能耗。

數據生存時間感知的神經網絡加速框架(RANA)。

2.1 訓練層次優化:數據生存時間感知的訓練方法

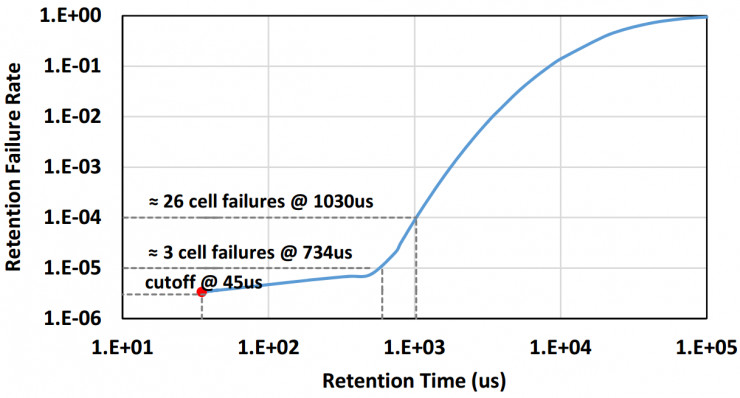

通常 eDRAM 的刷新週期會設置爲最差的存儲單元所對應的數據維持時間,以保證程序執行過程中所有存儲單元的數據都不會出錯。而在一個實際 eDRAM 存儲器中,不同存儲單元的數據維持時間是不同的。下圖是一條典型的 eDRAM 數據維持時間分佈曲線。橫軸是數據維持時間,縱軸是錯誤率,即低於給定維持時間的存儲單元佔所有存儲單元的比例。對於一個 32KB 的 eDRAM 而言,數據維持時間最短的存儲單元通常出現在 45 微秒處,對應的錯誤率大約爲 10^(-6) 量級。本文發現,適當增加數據維持時間,並不會顯著地提升錯誤率。

典型 eDRAM 數據維持時間分佈曲線。

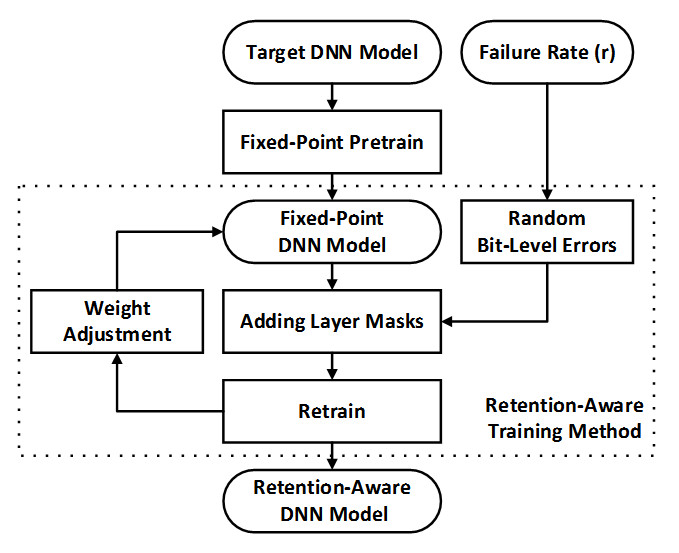

本文利用 DNN 的容錯能力來重新訓練網絡使其能承受更高的錯誤率,並獲得更長的「可容忍」的數據維持時間。如下圖所示,本方法在訓練的正向過程中對輸入和權重數據加入一個掩膜(Layer Mask)以引入誤差。這個掩膜會以一定的錯誤率對每個比特注入誤差。經過反覆的重訓練,如果最終的精度損失可以接受,那麼就認爲網絡可以承受當前的錯誤率。本文發現,對於 AlexNet、VGG、GoogLeNet 和 ResNet 四個網絡,錯誤率提高到 10^(-5) 後網絡精度仍沒有損失,此時對應的「可容忍」的數據維持時間提高到了 734 微秒,因此更有機會以更低的頻率刷新甚至消除刷新操作。

訓練層次優化:數據生存時間感知的訓練方法。

2.2 調度層次優化:神經網絡分層的混合計算模式

下圖所示是三種典型的計算模式,分別用多層循環的形式表示。本文發現,數據生存時間和片上存儲需求與循環順序,特別是最外層循環極爲相關。在輸入、輸出和權重這三類數據中,輸出數據的生存時間與另兩種數據類型完全不同。與輸入、權重這種靜態存儲在緩存中的數據不同,輸出數據會在累加的過程中不斷刷新。在每次刷新中,輸出數據會被重新寫入存儲器,對 eDRAM 存儲單元重新充電進而恢復了之前丟失的電荷。這一過程和週期性刷新操作本質上是一樣的。因此,如圖所示,如果把輸出數據作爲最外層循環迭代變量,數據生存時間將會非常短。當然,此時必須在片上存下全部的輸出數據以避免片外訪存。

三種典型的計算模式及其生存時間/緩存需求分析。

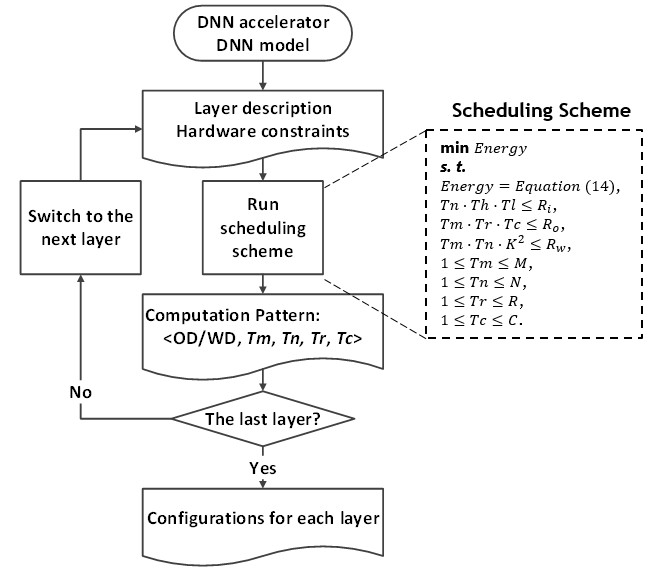

本文提出神經網絡分層的混合計算模式,根據芯片參數及 DNN 網絡參數,對網絡的每一層分配一個最優的計算模式。計算模式的探索過程被抽象爲一個目標爲系統能耗最小化的優化問題。具體調度方法如下圖所示,調度結果會被編譯成分層的配置信息(包括「可容忍」的數據維持時間、每層的計算模式及刷新標誌),以用於執行過程的硬件配置。

調度層次優化:神經網絡分層的混合計算模式。

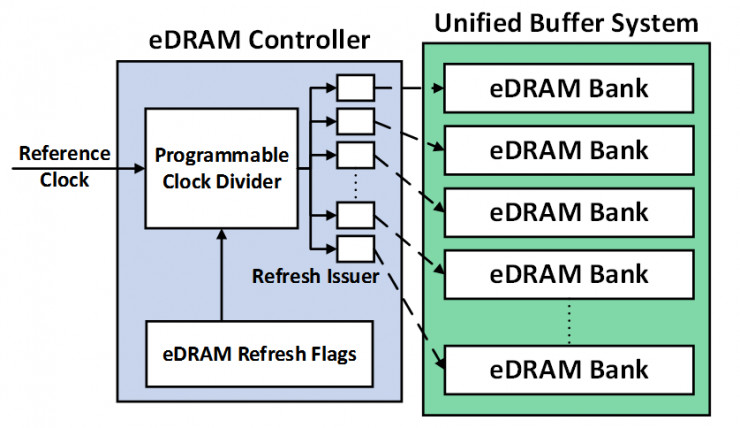

2.3 架構層次優化:刷新優化的 eDRAM 控制器

在傳統的 eDRAM 控制器中,所有的 eDRAM 分區都以最保守的刷新週期進行刷新。本工作對 eDRAM 控制器稍加改造,加入一個可編程的時鐘分頻器、各 eDRAM 分區獨立的刷新觸發器和刷新標誌位。控制器的配置信息來自於前兩個技術的編譯結果,具體將決定每個分區分別存儲什麼數據類型、是否需要刷新以及刷新週期。

架構層次優化:刷新優化的 eDRAM 控制器。

3 實驗結果

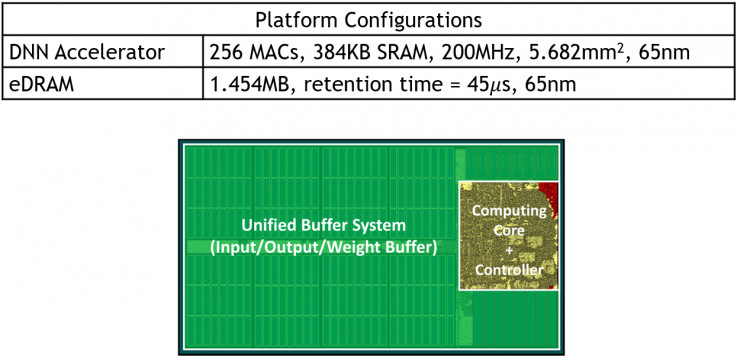

下圖爲用於驗證 RANA 框架的實驗平臺具體配置:本工作實現了一款 AI 計算芯片來進行 RTL 級別性能功耗分析,以獲得精確的性能參數和訪存行爲記錄。

驗證平臺配置參數及芯片版圖。

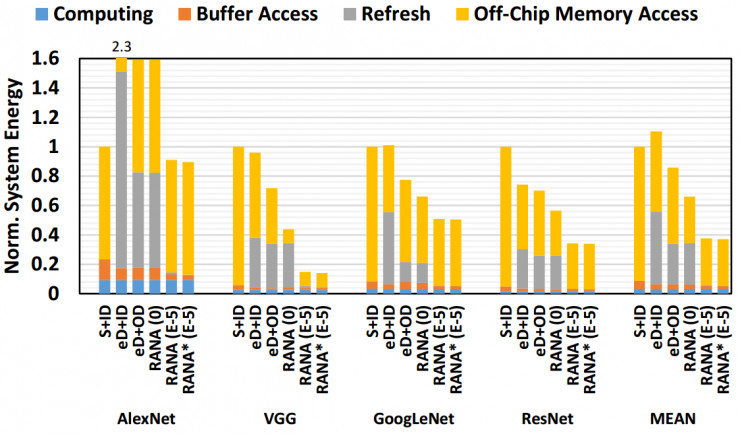

實驗結果顯示,RANA 框架可以消除 99.7% 的 eDRAM 刷新能耗開銷,而性能和精度損失可以忽略不計。相比於傳統的採用 SRAM 的 AI 計算芯片,使用 RANA 框架的基於 eDRAM 的計算芯片在面積開銷相同的情況下可以減少 41.7% 的片外訪存和 66.2% 的系統能耗,使 AI 計算系統的能量效率獲得大幅提高。

RANA 框架系統級能耗分析。

4 總結

清華大學微納電子系 Thinker 團隊近年來基於可重構計算架構設計了 Thinker 系列 AI 計算芯片(Thinker I,Thinker II,Thinker S),受到學術界和工業界的廣泛關注,在 2017 年曾獲得 ISLPED'17 低功耗設計競賽冠軍。Thinker 團隊此次研究成果,從存儲優化和軟硬件協同設計的角度大幅提升了芯片能量效率, 給 AI 計算芯片的架構演進提供了新思路。

相關閱讀:

論文第一作者塗鋒斌作爲 Thinker 芯片的核心架構設計者,曾作爲雷鋒網(公衆號:雷鋒網)分享嘉賓作客「硬創公開課」,介紹了他在神經網絡硬件架構的設計經驗。AI 科技評論圍繞分享內容整理成文:

清華大學博士生塗鋒斌:設計神經網絡硬件架構時,我們在思考些什麼?(上) | 硬創公開課總結

清華大學博士生塗鋒斌:設計神經網絡硬件架構時,我們在思考些什麼?(下) | 硬創公開課總結

在 6 月 29 日至 7 月 1 日舉行的 CCF-GAIR 2018 上,清華大學微電子所所長魏少軍教授將作爲 AI 芯片專場的學術嘉賓蒞臨現場做大會報告。